# Design and Verification of Layer 3 of OSI Model

T. S. Sagara Gouda<sup>1\*</sup>, S. M. Usha<sup>2</sup>

<sup>1</sup>M.Tech. Student, Department of Electronics and Communication Engineering, JSS Academy of Technical Education Bangalore, India <sup>2</sup>Associate Professor, Department of Electronics and Communication Engineering, JSS Academy of Technical Education Bangalore, India \*Corresponding author: lavanyasulake@gmail.com

Abstract: Directing is the way toward moving a bundle of information from source to goal and empowers messages to go starting with one PC then onto the next and in the end arrive at the objective machine. It is a bundle based convention. Switch drives the approaching parcel which originates from the info port to yield ports dependent on the location contained in the bundle. The switch has a one info port from which the parcel enters. It has three yield ports where the bundle is driven out. In this undertaking we are atomizing the elements of the Router by composing the code in VERILOG and recreating it in QUESTASIM. It is associated with at least two information lines from various systems (instead of a system switch, which interfaces information lines from one single system). This undertaking, basically underscores upon the Design and check of switch gadget, its high level engineering, and how different sub-modules of switch for example Register, FIFO, FSM and Synchronizer are orchestrated, and mimicked lastly associated with its top module.

Keywords: Router, Data packets, Verilog, Xilinx ISE.

#### 1. Introduction

A switch is a frameworks organization device that progresses data packages between PC frameworks. Changes play out the traffic planning limits on the Internet. A data pack is regularly sent beginning with one switch then onto the following switch through the frameworks that build up an internetwork until it shows up at its objective node. A switch is related with in any event two data lines from different frameworks. Exactly when a data package comes in on zone of the lines, the switch examines the framework address information in the group to choose an authoritative objective. By then, using information in zits directing table or controlling methodology, it manages the group to the accompanying framework on zits adventure.

### 2. Literature Survey

Link et al. [1] A switch is a systems administration gadget that advances information bundles between PC systems. Switches play out the traffic coordinating capacities on the Internet. An information parcel is normally sent starting with one switch then onto the next switch through the systems that comprise an internetwork until it arrives at its goal node. A switch is associated with at least two information lines from various networks. When an information bundle comes in on one of the lines, the switch peruses the system address data in the parcel to decide a definitive goal. At that point, utilizing data in its steering table or steering strategy, it guides the parcel to the following system on its excursion.

Link et al. [2] The test of the confirming an enormous plan is developing exponentially. There is a need to characterize new techniques that makes utilitarian check simple. A few systems in the ongoing years have been proposed to accomplish great practical check with less exertion. Late progression towards this objective is approaches. The technique characterizes a skeleton over which one can add fragile living creature and skin to their necessities to accomplish useful confirmation. OVM (open check approach) is one such productive philosophy and best thing about it will be, it is free. This ovm is based on system

Verilog and used effectively to achieve practicality reusability, speed of confirmation and so forth. This venture is planned for building a reusable test seat for checking 8 Port Router Protocol Bridge by utilizing framework Verilog and ovm. In this record the utilization of vmm and framework Verilog to confirm a structure and to build up a reusable test seat is clarified in bit by bit as characterized by check standards and philosophy. The test seat contains various parts and every segment is again made out of subcomponents, these segments and subcomponents can be reused for the future activities as long as the interface is same.

# 3. Methodology

Switch is planned and confirmed bit by bit, switch engineering is partition into sub modules every modules structured and checked independently and every one of them consolidated to frame a full high level design.

Every module is structured and checked utilizing Verilog code in the "Questa SIm" Environment and determination are checked with the yield waveform.

journals.resaim.com/ijresm | ISSN (Online): 2581-5792

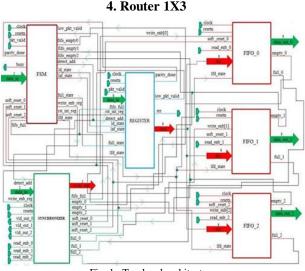

Fig. 1. Top level architecture

This plan comprises of 6 fundamental squares. Which are fsm\_router, router\_reg, ff\_sync, and 3 fifo. The fsm\_router square gives the control signs to the fifo, and router\_reg module.

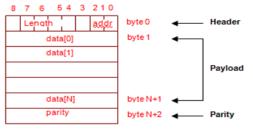

# A. Router packet

*Packet format:* the packet consists of 3 parts: Header, payload and parity each of 8-bit width and the length of the payload can be extended between 3 between 1 byte to 63 byte.

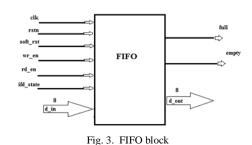

# B. Router: FIFO

Functionality

There are 3 fifo for each yield port, which stores the data starting from input port reliant on the control signals gave by fsm\_routermodule. fresetn is low by then full =0, void = 1 a data\_out = 0. Form action: The data from input data\_in is

analyzed at rising edge of the clock when input write\_enb is high and fifo isn't full. Get Operation: The data is scrutinized from yield data\_out at rising edge of the clock, when read\_enb is high and fifo isn't empty. ead and Write action should be conceivable at the same time. Full – it shows that all the territories inside fifo has been made. Void – it shows that all the zones of fifo are empty.

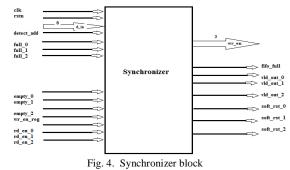

### C. Router: Synchronizer

#### **Functionality**

This module gives synchronization between switch FSM and switch FIFO modules. It gives faithful correspondence between the single data port and three yield ports. detect\_add and d\_in signals are utilized to choose a FIFO till a parcel steering is over for the chosen FIFO.

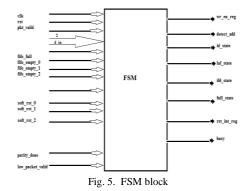

D. Router: FSM

'fsm\_router' module is the controller circuit for the router. This module creates all the control signals when new parcel is sent to switch. These control signals are utilized by different modules to send information at yield, composing information into the fifo.

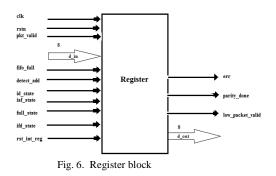

#### E. Router: Register

### Functionality:

This module actualizes 4 interior registers so as to hold a header byte, FIFO full state byte, inside equality and bundle equality byte. All the registers in this module are hooked on the rising edge of the clk.

The router\_reg module contains the status, information and equality registers for the router 1x3. These registers are locked to new status or info information through the control signals gave by the fsm\_router. This module contains status, information and equality registers required by switch.

Fig. 7. FIFO output waveform

Fig. 8. FSM Output waveform

Fig. 9. Sychronizer Output waveform

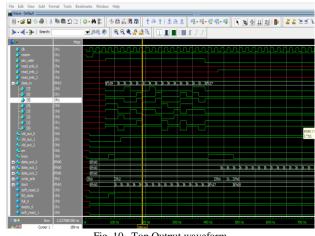

The result will be observed in questa sim simulation waveform according to the given conditions each module waveform observed separately.

Fig. 10. Top Output waveform

#### 6. Conclusion

In this we have structured and confirmed the Router1X3 center utilizing Verilog procedure utilizing Questasim. Many coding bugs are repaired during the confirmation. In this we have structured and confirmed the Router1X3 code utilizing Verilog, utilizing Questa sim. Many coding bugs are fixed during the check. This approach gives the total inclusion of the RTL plan of Router1X3.

#### References

- Salma Jabeen, Asarafuddin M D, "Design and Verification of Router 1x3 [1] Using UVM," 2017 International Journal for Research in Applied Science & Engineering Technology (IJRASET),

- Ch. Karthik, R. S. Uma Suseela "Design and Simulation Five Port Router [2] using Verilog HDL" 2015

- [3] International journal of VLSI system design communication systems, Pages 122-0126

- [4] Theodore Marescaux et. al. Interconnection Networks Enable Fine-Grain Dynamic Multi-Tasking on FPGAs. In FPL'2002, pages 795-805, September 2002.

- [5] M. Kumar, K. Kumar, S. K. Gupta and Y. Kumar, "FPGA based design of area efficient router architecture for Network on Chip (NoC)," 2016 International Conference on Computing, Communication and Automation (ICCCA), Noida, 2016, pp. 16001605.

- [6] R. Louis, M. Vinodhini and N. S. Murty, "Reliable router architecture with elastic buffer for NoC architecture," 2015 International Conference on VLSI Systems, Architecture, Technology and Applications (VLSI-SATA), Bangalore, 2015, pp. 1-4.

- [7] S. Malipatil and Rekha S, "Design and analysis of 10 port routers for network on chip (NoC)," 2015 International Conference on Pervasive Computing (ICPC), Pune, 2015, pp. 1-3.

- [8] N. Nasirian and M. Bayoumi, "Low-latency power-efficient adaptive router design for network-on-chip," 2015 28th IEEE International System-on-Chip Conference (SOCC), Beijing, 2015, pp. 287-291.

- [9] Qing Sun, Lijun Zhang and Anding Du, "Design and implementation of the wormhole virtual channel NoC router," 2015 4th International Conference on Computer Science and Network Technology (ICCSNT), Harbin, 2015, pp. 854-858.

- [10] S. Shenbagavalli and S. Karthikeyan, "An efficient low power NoC router architecture design," 2015 Online International Conference on Green Engineering and Technologies (IC-GET), Coimbatore, 2015,

5. Results

- [11] Y. Mrudula, V. Harshavardhan, G. Manu, Bhavana Godavarthi, "Design and Verification of Four Port Router for Network on Chip."

- [12] Ch. Karthik, R. S. Uma Suseela, "Design and Simulation Five Port Router using Verilog HDL," International journal of VLSI system design communication systems, pp. 0122-0126, 2015.